Микропроцессорная техника

Введение

В этой части рассматриваются

основы построения процессорной и микропроцессорной электроники. Мы не будем

описывать какие-либо устройство и работу реальных микропроцессоров, т.к. их существует

очень много, и, кроме того, есть немало специализированной литературы,

посвящённой тем или иным моделям процессоров или их семействам. Кроме того,

процессоры – устройства, в которых очень тесно переплетаются электроника и

программные аспекты.

Вместо этого

мы опишем общие принципы их функционирования, присущие всем им, вне зависимости

от их мощности, частоты, разрядности и пр. технических характеристик. Некоторые

аспекты могут отличаться от приведенного описания, но, в целом, суть всегда

одна и та же. Вопросы программирования также рассматриваться не будут, т.к.

выходят за рамки этой статьи.

Основная цель

любого процессора – обработка числовых данных. Здесь не будет идти речь о

специализированных цифровых сигнальных процессорах (DSP). В любом случае они

строятся на основе цифрового ядра, обрамлённого какими-то аналоговыми узлами

(АЦП, ОУ, компараторы, фильтры и т.д. и т.п).

Вначале, как

обычно, немного терминологии.

Процессор (центральный процессор, ЦП, англ. CPU – Central Processing Unit) – изначально и

дословно – вычислитель, исполнитель машинных инструкций (команд). Но d последнее

время это понятие очень разрослось, и им нередко называют достаточно большой

спектр конструкций и устройств – начиная от микропроцессоров в виде одной

микросхемы и заканчивая готовыми модулями, содержащими в своём составе и

процессор как таковой и какой-то набор вспомогательных периферийных устройств.

Микропроцессор – обычно одна микросхема, содержащая в себе все необходимые для работы узлы

(регистры, АЛУ, УУ).

Частота – частота тактовых сигналов, которые подаются на узлы процессора для

обеспечения его синхронизации.

Разрядность – кол-во бит данных, которое процессор может обработать за одну команду. Иногда

её определяют как ширину ШД процессора. За всю историю развития вычислительной

техники существовали (и существуют) 4, 8, 16, 32 и 64 разрядные процессоры. Но

следует иметь в виду, что здесь не так всё просто. Почти все 16 и 32 разрядные

процессоры имеют массу команд для обработки 8-битных данных, а 64-битные

способны обрабатывать и 32, и 16, и 8 разрядные данные. Даже процессоры,

позиционируемые фирмами-изготовителями как 8-битные, иногда могут производить

действия с 16-разрядными операндами. Так, например, достаточно древний

микропроцессор Z80 может обмениваться с памятью словами (2 байта) и производить

над ними арифметические действия, хоть он 8-разрядный. С шириной ШД тоже не так

всё просто. К примеру, широко известный процессор i8088 является полным клоном

16-разрядного i8086, с той лишь разницей, что у него 8-битная внешняя ШД.

Объём

адресуемой памяти – какое кол-во памяти может адресовать процессор. Максимальный

объём равен 2n,

где n – разрядность шины адреса ША. Но, в некоторых случаях, может быть меньше

этой величины.

Чипсет (англ. chipset) – набор микросхем поддержки процессора. В русскоязычной

литературе также распространён термин «микропроцессорный комплект». Ранее в

этот набор входил сам микропроцессор (либо микропроцессорные секции – см. ниже)

и все вспомогательные микросхемы – специализированные генераторы, интерфейсы,

какие-то регистры и пр.

Существуют и

другие понятия, они будет раскрываться по ходу повествования.

Раздел 1. Архитектура

микропроцессорных систем

Архитектура МП систем в

обобщённом виде имеет вид – рис. 1.

Рис. 1. Обобщённая архитектура

МП системы

Здесь:

каких-то временных данных;

работает процессор. Сюда относится всё – клавиатуры, интерфейсы, индикация

и пр.

Отметим, что

приведенная структура – классическая, и достаточно древняя. Современные

архитектуры имеют некоторые отличия и усовершенствования, призванные увеличить

быстродействие системы в целом. Но идеи и основные принципы их функционирования

ничем не отличаются от классического варианта.

Существует 2

основные варианта архитектур МП систем – гарвардская и Фон-Неймановская.

Гарвардская архитектура предполагает раздельное хранение программы и данных — рис. 2.

Рис. 2. Гарвардская

архитектура

Эта

архитектура предполагает, что программы, исполняемые CPU, хранятся ТОЛЬКО в ROM. Исполнять что-либо из RAM процессор не может. Т.е. RAM – 100% память

данных. Их так иногда и называют – память программ и память данных. В ROM тоже

могут храниться какие-то данные, но это могут быть лишь фиксированные

константы, определённые на этапе разработки программы. Изменяться в процессе

работы они не могут.

Физически ROM «сидит»

на своих собственных шинах, не связанных с общими шинами. Это несколько

ускоряет выполнение команд, т.к. процессор может распараллеливать работу с ROM/RAM,

но усложняет конечную схему и не позволяет «на лету» менять исполняемые программы

либо подгружать откуда-то новые.

Адресация ROM/RAM

совершенно разная, независимая друг от друга, и может частично или полностью

перекрываться. Т.е., например, ячейка с адресом 0 может существовать и в ROM, и

в RAM. Это не приводит к появлению каких-то ошибок, порче данных и пр.

По такой схеме

строятся многие микроконтроллеры (x51, AVR, PIC, …), в которых программа

(прошивка) хранится в ПЗУ микроконтроллера и не может быть изменена на ходу.

Фон-неймановская

архитектура совпадает c общей – рис. 1.

Фон-неймановский

процессор может исполнять программы из ROM и из RAM. Оба вида памяти находятся

в одном адресном пространстве процессора и абсолютно равнозначны для процессора.

При этом он даже сам «не знает», откуда «родом» программа, которую он выполняет.

При этом процессор может совершенно безболезненно переходить ROM<->RAM, что

широко используется для организации в ROM различных стандартных библиотек

функций и пр. Попытки записи в ROM не вызывают никаких ошибок, подобные операции

просто игнорируются соответствующими микросхемами.

Данные и

программы хранятся в одной и той же памяти, они никак не отличимы друг от

друга, просто разнесены по разным адресам. Потому, такие процессоры способны

полноценно исполнять любые данные как программу, что повсеместно применяется

для загрузки в память программ из каких-то внешних носителей.

ROM и RAM должны

быть аппаратно разнесены по разным (непересекающимся) адресам памяти, иначе

данные, считываемые из них неизбежно «перемешаются» на общей ШД и возникнут

ошибки.

Недостатки

архитектуры – невозможность распараллелить выборку команд и данных (решается

введением системы очередей команд и различного кэширования), возможность

исполнить данные, не являющиеся программой как программу (разные процессоры

защищаются от этого по-разному)). Но, несмотря на эти недостатки, данная

архитектура очень широко распространена.

Так, очень

многие процессоры, начиная, например, от очень старых i8080, Z80 и заканчивая

современными Core i5, i7 и т.д. и т.п. имеют фон-неймановскую архитектуру. Кроме

того, в основе многих ARM микроконтроллеров лежит фон-неймановское ядро.

RISC и CISC

процессоры

RISC –

Reduced Instruction Set computer – дословно – компьютер с упрощённым

(урезанным) набором команд.

В таких

процессорах используется система таких команд, которые ядро процессора может максимально

быстро декодировать и исполнить. В таких системах команд обычно отсутствуют

сложные команды типа деления, умножения, а также команды, извлекающие

операнд(ы) из памяти, что-то с ними выполняющие и возвращающие результат

обратно в память. Такие операции необходимо разбивать на несколько простых,

типа «загрузить операнд 1 из памяти в регистр A», «загрузить операнд 2 из

памяти в регистр B», «сложить содержимое регистров A и B, поместив сумму в

регистр C», «передать содержимое регистра C в память» и пр.

CISC –

Complex Instruction Set computer – дословно – компьютер с комплексным набором

команд.

Система команд

характеризуется разной длиной команды, наличием сложных команд (деление,

умножение, возможность работы с памятью одновременно с какой-либо операцией) и

пр. Но, в то же время, в CISC архитектурах есть и простые «RISC» команды и

никто не запрещает «писать программы в стиле RISC».

Но в

современном мире грани между RISC и CISC постепенно стираются. Так, например, многие

современные RISC процессоры (это, в основном, микроконтроллеры) имеют составе

своей системы команд умножение и деление целых чисел, хоть эти операции по

определению являются частью CISC архитектур и т.д.

Микропроцессоры

и микроконтроллеры

Несмотря на то,

что многие путают эти понятия, часто называя микроконтроллер микропроцессором,

или просто процессором, это несколько разные вещи и между ними есть довольно

существенная разница.

Процессор и

микропроцессор – ЭВМ общего назначения, т.е. это 100% вычислитель, в нём

нет никакой памяти (кроме некоторого минимально необходимого количества

регистров) – ни ROM, ни RAM, ни какой-либо периферии, ни даже тактового

генератора. Т.е. любая система (даже самая простейшая) на базе микропроцессора

в обязательном порядке должна содержать, кроме самого микропроцессора, тактовый

генератор, ROM и RAM, пусть даже каких-то минимальных объёмов.

Любой микроконтроллер (МК) – ЭВМ специального назначения. Он всегда содержит в своём составе и

генератор, и ROM с программой, и RAM, и некоторую периферию (таймеры-счётчики,

АЦП и пр.). Потому он, в принципе, всегда работоспособен сам по себе, без

каких-либо внешних схем и узлов. Также в МК обычно гораздо больше регистров по

сравнению с обычными микропроцессорами.

Секционные

процессоры или процессорные секции

Процессорные

секции обычно не являются процессорами в прямом смысле этого термина. Как

правило это просто АЛУ и набор каких-то необходимых регистров и возможностью

объединения в цепочки для наращивания разрядности. Они не содержат средств

работы с памятью, выборки команд и пр. Для построения на их основе полноценного

процессора необходима разработка устройства управления и прочих узлов.

Также,

микропроцессорные комплекты, содержащие секции часто содержат в себе некоторые

узкоспециализированные микросхемы (например, схемы ускоренного переноса для

повышения быстродействия многоразрядных процессоров на базе этих секций). Здесь

мы не будем рассматривать эти вопросы.

Раздел 2. Внутренняя

архитектура процессоров

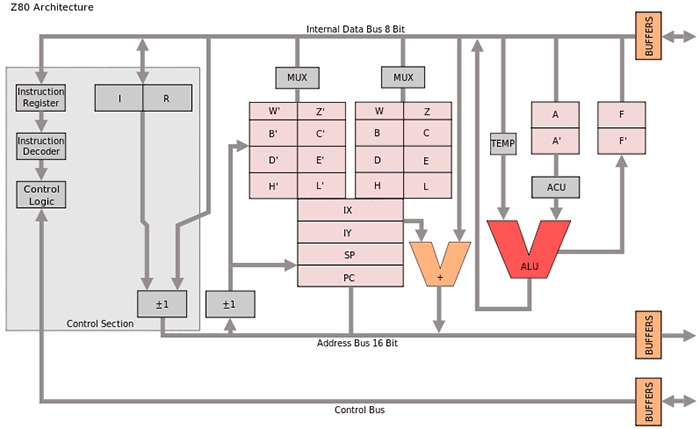

Рассмотрим

внутреннюю архитектуру процессора на примере микропроцессора Z80 – рис. 3.

Рис. 3. Архитектура

процессора Z80 (с сайта Википедии)

Конечно,

разные процессоры имеют разную архитектуру, разный набор внутренних регистров и

пр., но основные моменты остаются неизменны.

Основные узлы

процессора – АЛУ, набор регистров (розовые прямоугольники на схеме),

управляющее устройство и вспомогательные узлы.

«Сердце»

процессора – АЛУ (арифметико-логическое устройство, англ. ALU). Именно оно

выполняет 95% всех операций. Регистры хранят небольшой объём текущих данных, с

которыми работает процессор. Управляющее устройство обеспечивает управление

узлами процессора, работу с памятью и декодирование команд.

Разрядность

каждого регистра совпадает с разрядностью ШД процессора, хотя это не всегда

так. Очень часто регистры могут попарно «объединяться», образуя регистры

удвоенной или учетверённой разрядности. Так, например, в том же Z80 8-разрядные

регистры B/C, D/E, и H/L могут использоваться как по отдельности, так и в виде

16-разрядных регистров BC, DE и HL.

Среди

регистров, хранящих данные, часто один стоит «особняком». Это т.н. аккумулятор.

На рис. 3 это регистр A. Его особенность заключается в том, что он всегда

представляет собой один из операндов любой операции, выполняемой АЛУ, и всегда

служит получателем результата любой операции. В более развитых структурах (и во

многих микроконтроллерах) аккумулятором может служить любой другой регистр. Аккумулятор

тоже может быть разной разрядности.

Регистр F – регистр

флагов. Этот регистр никогда не принимает никакого участия в обмене данными, он

содержит набор битов, которые показывают состояние АЛУ, а также позволяют

управлять поведением процессора в различных ситуациях. Разрядность регистра

флагов, в принципе, никак не связана с разрядностью самого процессора, т.к.

кол-во флагов обычно гораздо меньше тех же 16, 32 или даже 8 бит данных,

которые способен обрабатывать процессор. Но, тем не менее, его разрядность

обычно такая же, как и разрядность остальных регистров. Это делается просто для

удобства программирования.

Вот наиболее

часто встречающихся флагов:

Z (ZF) – флаг

нуля (zero flag). Устанавливается в 1, если результат любой операции равен

нулю.

C (CF) – флаг

переноса (carry flag). Для операций сложения/вычитания показывает перенос/заём,

при операциях сдвига используется как доп. бит – см. раздел 3.

P (PF) – флаг

чётности (parity flag). Устанавливается в 1, если результат операции содержит

чётное кол-во единичных битов. Не путать с чётными/нечётными числами! Это

совершенно разные вещи.

S (SF) – флаг

знака (sign flag). Равен 1, если результат отрицательный (меньше нуля). Если 0,

либо больше нуля, то флаг равен 0. По сути этот флаг – копия знакового бита – см.

раздел 3.

I (IF) – флаг

разрешения прерываний (interrupt flag). Если равен 1, то процессор будет

реагировать на прерывания – см. специализированную литературу. 0 – прерывания

запрещены.

AC – флаг

дополнительного переноса (auxiliary carry flag). То же самое, что и CF, но

показывает перенос/заём между «половинками» операндов. Если, например,

складываются 8-битные числа, то AC покажет перенос между 3 и 4 битами.

OF — переполнение

(overflow flag). 1 свидетельствует о переполнении разрядной сетки. Иными

словами – слишком большой или слишком маленький результат.

Существуют

также и другие флаги.

Раздел 3. Типы

данных и операции, выполняемые АЛУ

Перед тем, как

рассматривать внутреннюю структуру АЛУ, необходимо сказать несколько слов об

операциях, выполняемых им и о типах данных. С одной стороны может показаться,

что эта тема относится к программированию, а не к электронике, но, в то же

время, без понимания этих вещей сложно представить себе работу всего процессора

в целом.

Начнём с типов

данных.

Все числа,

обрабатываемые процессорами можно разбить на 2 категории (как, собственно и в математике)

– целые и вещественные.

Вещественные

числа мы рассматривать не будем, т.к. они часто обрабатываются не основным АЛУ,

а специализированными устройствами (различными арифметическими сопроцессорами),

да и все алгоритмы операций над такими числами всегда сводятся к целочисленным

операциям. В специализированной литературе по программированию старых

8-разрядных процессоров типа i8080, K580, Z80 и аналогичных эти алгоритмы

описаны достаточно хорошо, а их аппаратные реализации не сильно отличаются от

программных.

В свою очередь,

целые числа делятся на знаковые и беззнаковые. Такое деление обусловлено

разными форматами хранения этих чисел, а также некоторыми нюансами их

обработки. Беззнаковые числа и ноль всегда считаются положительными.

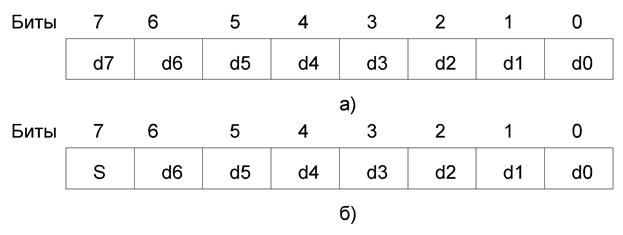

На рис. 4 представлен

общий формат знаковых и беззнаковых чисел.

Рис. 4. Формат

8-битных беззнаковых (а) и знаковых (б) чисел

Видно, что в

беззнаковом формате все биты отводятся под число, а в знаковом формате старший

бит показывает знак числа. Этот бит называют знаковым битом.

При этом принято

S=0 для положительных чисел и нуля, S=1 для отрицательных. Также можно

заметить, что n-разрядное беззнаковое число может находиться в диапазоне от 0

до 2n-1, а

знаковое – от -2n-1 до +2n-1.

К примеру, беззнаковое 8-битное число лежит в диапазоне 0..255, а знаковое -127

.. +127.

Числа со

знаком могут быть представлены в трёх разных видах – прямой код (ПК), обратный

код (ОК) и дополнительный код (ДК). Рассмотрим их.

Прямой

код (ПК)

Число хранится

«как есть», т.е. в битах d6-d0 всегда записан модуль числа в неизменном виде,

меняется лишь бит S, задавая знак числа. Это самый простой и наглядный способ,

однако он крайне неудобен при выполнении различных операций (для сложения и

вычитания требуются разные схемы, результирующий перенос надо брать не из

старшего разряда, а из предыдущего, сложно формировать знак результата и т.п.)

и, поэтому, нигде не применяется.

Обратный

код (ОК)

Положительные

числа хранятся в ПК, модуль отрицательных чисел хранится в инвертированном

виде. К примеру: +15= 00001111, -107= 10010100. Старший бит – знак, все

остальные биты числа -107 проинвертированы (для примера +107=01101011). Здесь

имеет место особенность: существует два нуля – положительный (00000000) и

отрицательный (11111111). При работе с ОК это следует иметь в виду.

Дополнительный

код (ДК)

Положительные

числа хранятся в ПК, модуль отрицательных чисел хранится в инвертированном виде

+1. К примеру: -107= 10010101. Старший бит – знак, все остальные биты числа -107

проинвертированы, и к инверсии прибавлена 1. Здесь ноль, как и положено, лишь

один – положительный.

Многобайтовые

числа

Как видно,

один байт – очень малая величина для многих применений. Даже результат простого

сложения 2-х однобайтовых чисел очень часто может выйти за границу 8-байтов,

не говоря уж об умножении.

АЛУ может

выполнять операции над операндами лишь определённой длины, которая задаётся

разрядностью конкретного процессора и набором его команд. Как правило это 8,

16, 32 или 64 бита. Для более длинных чисел применяются специальные программные

алгоритмы.

Почти все

процессоры имеют команды для работы с данными, находящимися в RAM/ ROM системы.

Если размещение одного байта в памяти вполне очевидно и однозначно, то с многобайтными

числами возможны варианты.

В настоящее

время общепринятыми являются 2 варианта размещения байтов в памяти:

1. Младшими

байтами вперёд. Младший байт числа занимает в памяти меньший адрес (т.е. идёт

первым). К примеру, 4-байтовое число 98675FDFh (в шестнадцатеричном виде) будет

размещено «задом наперёд»: DFh, 5Fh, 67h, 98h. Эта схема получила название

«маленький индеец» (англ. little endian) или обратный порядок байтов.

2. Старшими

байтами вперёд. Младший байт занимает больший адрес. То же самое число 98675FDFh

будет записано в память как 98h, 67h, 5Fh, DFh. Этот способ называется «большой

индеец» (англ. big endian), прямой порядок байтов.

При этом порядок

битов в каждом байте никогда не меняется.

В системе маленького

индейца работают, например, все процессоры Intel, AMD, микроконтроллеры Atmel

AVR, ARM и т.д.

Большого

индейца используют некоторые процессоры фирм IBM, Motorola, SPARC.

Примеры

выполнения операций сложения/вычитания над числами в ОК и ДК очень

подробно рассмотрены в [1]. Мы не будем здесь их повторять.

Из этих примеров

видно, что благодаря использованию этих кодов вычитатель не требуется (достаточно

одного сумматора), что несколько упрощает АЛУ процессора. Но, т.к. операции в

ДК выполняются проще и быстрее, то именно этот вид кодирования стал стандартом

де-факто и применяется во всех процессорах, контроллерах и пр.

Умножение и

деление, как уже указывалось выше, являются сложными составными операциями,

состоящими из цикла, в котором определённое кол-во раз повторяются операции

сложения (для умножения) / вычитания (для деления) и сдвига (см. ниже). Существует

несколько основных алгоритмов выполнения этих операций – [2], [3]. Для умножения

существует и несколько видоизменённых, т.н. «ускоренных» версий алгоритма,

наиболее распространённая – алгоритм Бута – [4].

Ускорения основаны

на том, что на каждом шаге обычный алгоритм всегда анализирует один бит множителя,

а ускоренные – 2 бита. Но подобный подход оправдан в аппаратных реализациях, в

программных же он лишь усложнит и запутает программу.

Следует

отметить, что не всегда процессоры имеют возможность аппаратного умножения.

Логические

операции – AND, OR, NOT, XOR. Ничем не отличаются от простых однобитовых

операций, рассмотренных в 1-й части статьи. Знак числа в этих операциях никогда

не учитывается, все биты операндов обрабатываются совершенно независимо друг от

друга.

Сдвиг. Операция,

при которой биты числа сдвигаются вправо или влево на один или более бит – [5].

Всегда имеет один операнд.

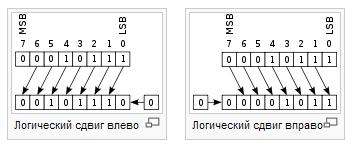

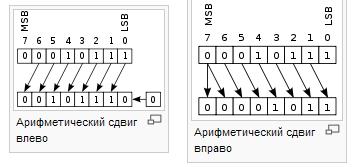

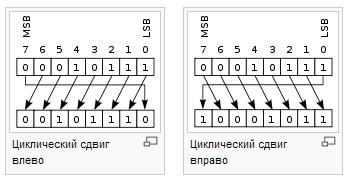

Кроме

направления сдвиги разделяются на несколько подвидов: логические (рис. 5), арифметические

(рис 6) и циклические (рис 7).

Рис.5. Логический

сдвиг

Рис. 6.

Арифметический сдвиг

Рис.

7. Циклический сдвиг

Как видно, сдвиги

– простейшие логические операции, для выполнения которых даже не нужны никакие

логические схемы. Сдвигатели на один разряд – просто набор проводов. Некоторые

процессоры могут сдвигать операнд на несколько бит. Схемотехника подобного

сдвигателя может быть разной, начиная от набора однобитовых сдвигателей и

заканчивая некими специальными лог. схемами.

В операциях

сдвига всегда очень широко используется вышеупоминавшийся флаг переноса C (CF).

При сдвиге в освобождающийся бит заносится значение этого флага, а также,

выпадающий слева или справа бит не теряется, а попадает в CF, что позволяет его

далее анализировать. В ряде случаев подобный подход может оказаться проще, чем,

например, проверять биты операцией AND с какими-то масками.

Операции

сдвига могут служить и простыми и быстрыми операциями деления и умножения. Дело

в том, что сдвиг любого числа влево на один разряд эквивалентен умножению его

на 2, вправо – делению на 2.

Арифметические

сдвиги применяются при работе со знаковыми числами.

Прочие

операции. Ряд процессоров могут содержать какие-то дополнительные операции,

например, манипулирования отдельными битами (очень часто встречается в

микроконтроллерах), операции с многобайтными числами, циклический сдвиг числа

через флаг переноса (например, сдвигаемый 8-разрядный регистр совместно с

флагом CF представляется как 9-разрядный и сдвигается как 9-разрядный) и пр.

Программы,

машинные коды и язык ассемблера.

Поведение

любого процессора (микропроцессора, микроконтроллера) всегда задаётся

программой. Без программы процессор совершенно неработоспособен.

Программа с

точки зрения процессора – просто набор байтов, которые он интерпретирует как

команды и исполняет их.

Набор команд,

их кодировка, формат и пр. всегда разные у разных процессоров. Конечно,

существуют семейства схожих друг с другом процессоров, имеющих одни и те же

команды в одном и том же формате, но разные модели процессоров могут иметь некоторые

дополнительные команды и пр. К примеру, семейство процессоров Intel x86 включает

в себя достаточно много конкретных моделей (8086, 8088, 80286, 80386 и т.д и

т.п), а также великое множество их аналогов других фирм-разработчиков. При

этом действует одно общее правило – более старший процессор всегда может

выполнить программу, написанную для более младшего, но не наоборот. Так,

например, 80286 процессор всегда выполнит программу для 8086 процессора, а

8086-й выполнить программу для 80286 может далеко не всегда, т.к. 80286 имеет

множество дополнительных команд и возможностей, которых в 8086 просто нет и

т.д.

Также следует

иметь в виду то, что структуры и схемы конкретных вычислительных систем могут

отличаться, даже если они построены на близких процессорах (или даже на одном и

том же процессоре). Более подробно – см. раздел 5.

Набор байтов

программы иногда называют машинными кодами.

Т.к.

человеку-программисту крайне неудобно работать непосредственно с кодами команд,

то был разработан специальный язык программирования – ассемблер. В

основе языка ассемблера лежат некие словесные эквиваленты машинных кодов. При

этом приняты ряд достаточно удобных правил – регистры и флаги обозначаются именами,

команда, например, сложения всегда называется, например, add, независимо от

того, что она складывает – регистр с регистром или регистр с константой и пр.

Конечно,

следует чётко знать и понимать, что и машинные коды, и соответствующий им язык

ассемблера всегда жёстко привязаны к конкретной архитектуре либо модели

процессора. Потому, если мы, например возьмём программу, работающую, например,

на процессоре i8086 и без каких-либо изменений запустим её на каком-нибудь

микроконтроллере Atmel AVR (или наоборот), то работать она не будет, т.к. это

две совершенно разные архитектуры и два совершенно разных процессора. Даже

несмотря на то, что они оба во многом похожи друг на друга – умеют складывать и

вычитать числа, выполнять какие-то переходы в памяти и пр.

Раздел 4. Структура

АЛУ

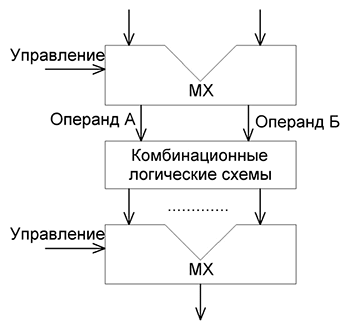

В общем случае

АЛУ это набор отдельных логических схем (сумматоры, сдвигатели и пр.). На

входах АЛУ часто установлены мультиплексоры, позволяющие подавать на тот или

иной вход АЛУ данные из разных источников (внутренние регистры, ШД и т.д.).

Выходы схем заводятся на выходной мультиплексор, который собственно и

определяет выполняемую АЛУ операцию.

Разрядность

всех схем и мультиплексоров обычно одинакова.

Управляющее

устройство процессора всегда задаёт тип операции (активизируя одну из логических

схем), управляет входными/выходными мультиплексорами и пр.

Примерная

(обобщённая) структура АЛУ показана на рис. 8.

Рис. 8. Обобщённая

структура АЛУ.

Верхний мультиплексор

обеспечивает подачу в логическую часть АЛУ входных данных из разных источников,

нижний выдаёт на выходную шину результат из той или иной схемы. По сути, именно

нижний мультиплексор определяет операцию, выполняемую АЛУ.

Отметим ещё

раз, что конкретная структура АЛУ у разных процессоров разная, может включать

различные дополнительные компоненты.

Так, например,

в старых микропроцессорных секциях (например, К1804ВС1/ВС2) на выходе АЛУ

довольно часто встречался дополнительный сдвиговый регистр, который упрощал

реализацию алгоритмов умножения/деления и ускорял эти операции за счёт того,

что АЛУ могло выполнять одновременно 2 операции – сложение/вычитание и сдвиг

влево/вправо. А т.к. именно такие пары используются при умножении/делении, то

эти действия можно было выполнить одной командой, а не двумя, что несколько

ускоряло эти операции.

В современных

процессорах АЛУ гораздо более сложное. Так, современные процессоры Intel имеют

специальные команды, обрабатывающие одновременно не 2 операнда, а больше,

способны работать с плавающей точкой и т.д. и т.п.

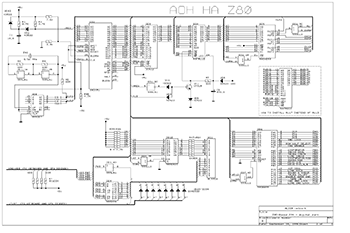

Раздел 5. Пример схемы

с использованием микропроцессора

В завершение

данной части рассмотрим основные вопросы и аспекты построения микропроцессорных

систем на примере АОНа на Z80. Данная конструкция была популярна в 80-90 х

годах прошлого века. Несмотря на её древность и, м.б. нынешнюю неактуальность, на

ней очень отчётливо видны все основные моменты построения подобных систем.

Мы не будем

рассматривать целиком всю схему этого АОНа, это выходит за рамки статьи,

рассмотрим лишь его процессорную часть – рис. 9.

Рис. 9. Схема

процессорной части АОНа на Z80.

На схеме мы

видим:

C1, R1 и пр. Цель этого узла – сбросить процессор в начальное состояние

при включении питания. Стоит отметить, что многие микроконтроллеры уже

имеют родственную схему в своём составе, поэтому делать эту схему для них

необязательно.

частотой 4 MHz для процессора – DD1.1, DD1.2, DD8 и окружающая

«рассыпуха». Счётчик DD8, в принципе не нужен, он используется просто как

делитель частоты, если используются разные задающие кварцы.

программу, по которой работает процессор.

процессором для хранения рабочих данных.

микросхема-таймер.

И т.д.

Из схемы видны

следующие особенности:

— ШД

процессора (сигналы D0-D7 на общей шине схемы) подключается одновременно ко

всем компонентам системы (RAM, ROM, все периферийные микросхемы).

— ША (сигналы A0-A15

на общей шине схемы) подключена к ROM, RAM и к ряду других узлов.

— ШУ включает

в себя сигналы MREQ, IORQ, RD, WR.

— Резисторы R39-R46

обеспечивают нагрузочную способность ШД и позволяют «не думать» о

входных-выходных токах, количестве и типах микросхем, «сидящих» на ШД. Такие

же резисторы нередко устанавливают и на шине адреса.

Работа с

памятью и периферийными устройствами

Процессор

обращается к памяти и ко всем периферийным устройствам (ПУ) с помощью одних и

тех же шин данных и адреса. Т.е. ША может указывать как адрес ячейки в памяти, так

и адрес какого-то ПУ.

Память/ПУ

различаются с помощью инверсных сигналов MREQ и IORQ. MREQ=0 означает, что процессор

обращается к памяти. IORQ=0 – обращение к ПУ.

Потому на

микросхемы ROM/RAM так или иначе заводятся сигнал MREQ, а на узлы периферии – сигнал

IORQ.

Инверсные

сигналы RD и WR показывают, какую операцию проводит CPU – чтение (RD=0), либо

запись (WR=0).

Эти сигналы

инверсные у всех процессоров и у всех микросхем, поэтому никогда не возникает

каких-либо сложностей с их стыковкой.

Выбор (активизация)

тех или иных микросхем происходит сигналами выборки CS (Chip Select). Они всегда

инверсные, т.е. когда CS =1, микросхема неактивна (не реагирует на другие сигналы,

её ШД в 3 состоянии), а когда CS = 0, она активизируется, реагирует на остальные

сигналы и передаёт/принимает данные процессора.

В

«полноценных» схемах эти сигналы формируются специальным адресным дешифратором,

который формирует CS той или иной микросхемы лишь в одном-единственном случае,

когда на ША появится нужный адрес. Это исключает разного рода ложные

срабатывания.

Схема на рис.9

в этом смысле является сильно упрощённой, для формирования сигналов CS используются элементы ИЛИ DD1.1A, DD7.2B, DD7.4B. Такое решение, конечно, проще и дешевле

полного адресного дешифратора, учитывающего состояние всех 16 линий ША, но приводит

к тому, что, например, DD5 будет активизироваться при любом адресе, в

котором линия A6=0. Т.е. она имеет не один адрес, а много. Потому такой способ

годится при построении относительно простых, фиксированных схем, не предполагающих

добавление каких-либо узлов и, в общем случае, считается существенным

недостатком.

Можно

заметить, что на микросхемы DD5 и DD6 заведены линии A3 и A4 ША. Это означает,

что в самих микросхемах есть до 4 разных регистров, которые адресуются разными

сочетаниями значений на этих линиях. Их дешифрация выполняется в самих

микросхемах. Потому, 4 адреса 1111111110100xxx .. 1111111110111xxx относятся к

микросхеме DD5. Стоит отметить, что обычно для этих целей используются линии A1

и A0.

Более подробно

– см. специализированную литературу по микропроцессорам и МП системам.

Ссылки:

компьютер выполняет арифметические действия над целыми числами

умножения

умножения Бута (Википедия)

сдвиг

Автор: Павел Негробов (hd44780)